|

|

Seminar "ddb1"

Design Digitaler Baugruppen unter Berücksichtigung von Signal- und Power Integrity Aspekten

|

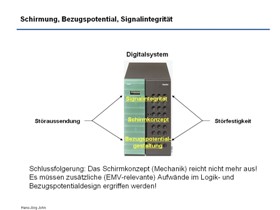

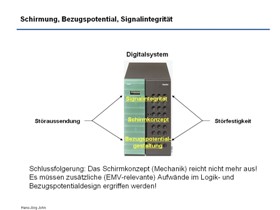

Einflußgrößen auf EMV

Digitale Systeme müssen sowohl Forderungen zur Störfestigkeit als auch Störemission genügen.

Diese Forderungen lassen sich in der Regel nicht mehr mit einem geschlossenen Schirm erfüllen.

|

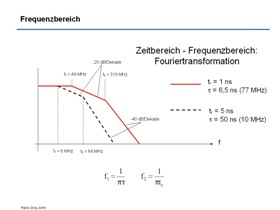

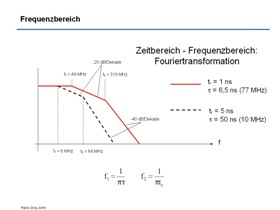

Zeit- und Frequenzbereich

Die Zeitparameter digitaler Signale stehen in einem unmittelbaren Zusammenhang zum Frequenz-bereich (Fouriertransformation). Dieser Zusammenhang hat Auswirkungen auf das ausgesendete Spektrum.

|

|

|

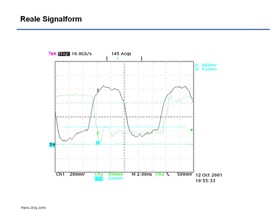

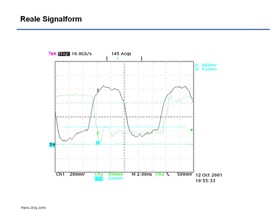

Reale Signale

An Hand realer Signalformen können Konsequenzen zur Funktion aufgezeigt werden. Die Interpretation realer Signalverläufe gibt Hinweise auf mögliche Designfehler.

|

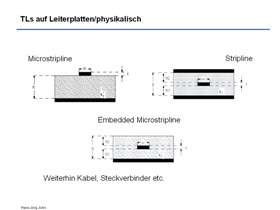

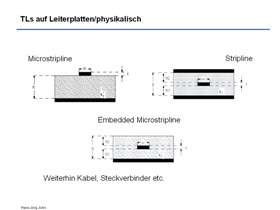

Leitungen auf PCBs

Microstripline, Embedded Micro-stripline und Stripline.

Definition auf Grund der Lage des Leiterzuges in der Leiterplatte.

Konsequenzen auf die Berechnung von Impedanzen.

|

|

|

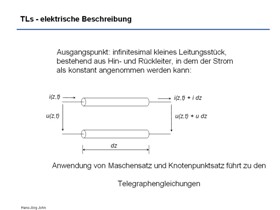

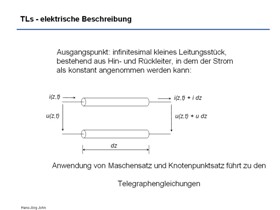

Ersatzschaltbild einer Leitung

Ersatzschaltbilder zur Ableitung der Telegraphengleichungen. Widerstandsbelag und Induktivitätsbelag.

Ableitungsbelag und Kapazitätsbelag.

Primäre Leitungsparameter und sekundäre Leitungsparameter.

|

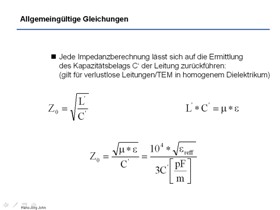

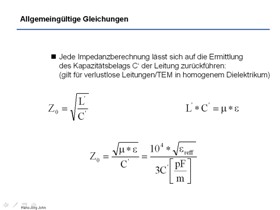

Wellenwiderstand, verlustlos

Die Berechnung des Wellenwiderstandes für Leitungen in Leiterplatten im verlustlosen Fall wird auf die Ermittlung des Kapazitätsbelages zurückgeführt.

|

|

|

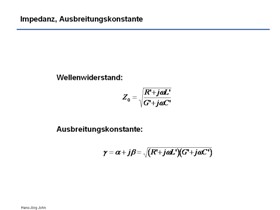

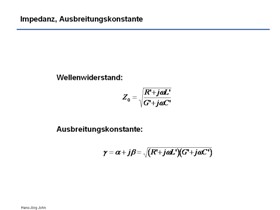

Wellenwiderstand, verlustbehaftet

Komplexe Größe, bestehend aus Real- und Imaginärteil bzw. Betrag und Phase.

Frequenzabhängige Ausbreitungskonstante.

|

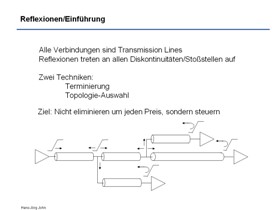

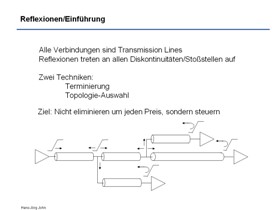

Reflexionen 1

Analogie zu Wasserwellen und Stoßstellen sowie transmittierte und reflektierte Anteile.

Ein- und Ausgangswiderstände von integrierten Schaltkreisen.

Flankensteilheiten digitaler Signale.

|

|

|

Reflexionen 2

Leitungssysteme, Stichleitungen, Sternpunkte.

Daisy-Chain-Verdrahtung.

Terminierungen.

Hin- und rücklaufende Wellen.

|

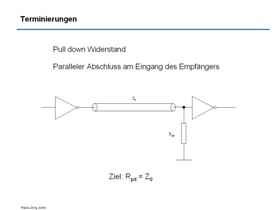

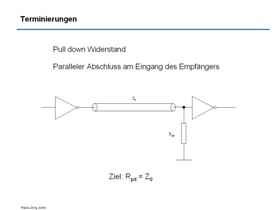

Terminierungsstrategien

Serienterminierung.

Terminierung mit Pull-Up und Pull-Down-Strategien.

Thevenin-Terminierung. Diodenterminierung.

Ein- und Ausgangswiderstände digitaler Schaltkreise.

|

|

|

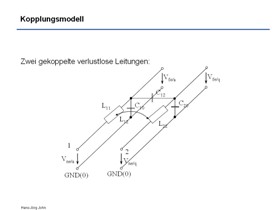

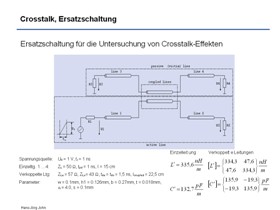

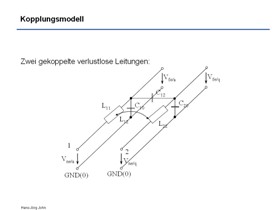

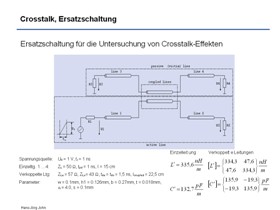

Crosstalk 1

Ersatzschaltungen unabhängig von der Geometrie der Kopplung in der Leiterplatte.

Berechnung diverser Kenngrößen.

Ermittlung der Koppelkapazität.

Größenordnungen der zu erwartenden Gegeninduktivitäten. Leitungsmatrizen.

|

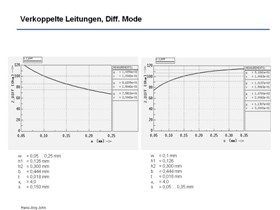

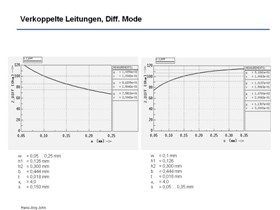

Crosstalk 2

Verkoppelter Leitungsbereich und unverkoppelter Bereich.

Störende Leitung und gestörte Leitung.

Forward- und Backward-Kopplung.

Common Mode und Even Mode.

|

|

|

Differenzielle Impedanz

Verkoppelte Leitungsführung. Gegenphasige Ansteuerung.

Etch side coupling und Broad side coupling.

Regeln für die Clearance. Vorteile des Pair routings.

Informationen zu Fieldsolvern.

|

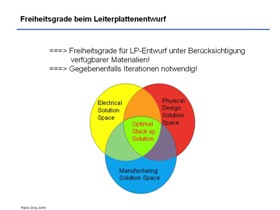

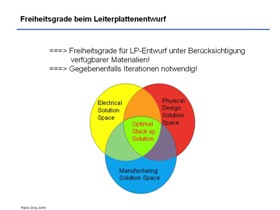

Definition von Lagenaufbauten

Elektrische Einflussgrößen: Impedanz, Kopplung, ...

Physikalische Einflussgrößen:

Verdrahtungsdichte, Lagenanzahl ...

Technologische Einflussgrößen:

Pressparameter, Ätztoleranzen ..

|

|

|

Impedanz bestückter PCB

Auswirkungen der Bestückung auf die Impedanz.

Unterschiedliche Netztopologien.

Die Eingangskapazität integrierter Schaltkreise.

Die Simulation von Signalverläufen.

|

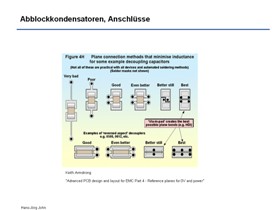

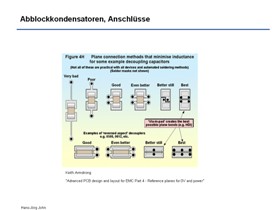

Abblockkondensatoren

Stromversorgungssysteme.

Die Stromaufnahme digitaler Schaltungen.

Parasitäre Größen von üblichen Kondensatoren.

Die sinnvolle Pad-Gestaltung von Kondensatoren.

Buried Capacitance.

|

|

|

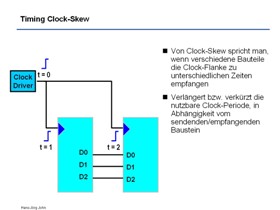

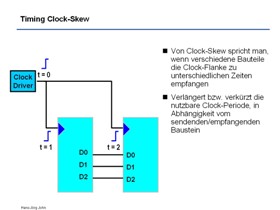

Timing

Die Interpretation von Datenblattangaben.

Timing Parameter (Skew, Jitter, Laufzeit, Set Up, Hold, Clock to Output).

Common Clock Systeme.

Timing-Gleichungen.

|

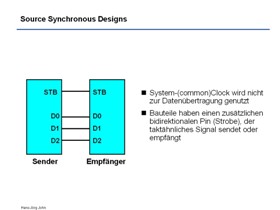

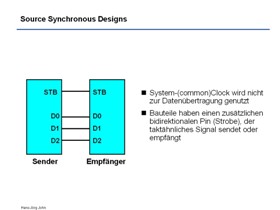

Source Synchronous Design

Wirkungsweise Vorteile und Grenzen., Einflussgrößen. Timing-Gleichungen.

|

|

|

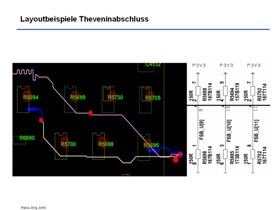

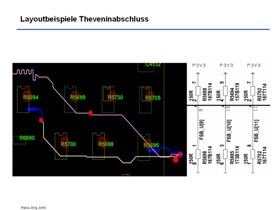

Layoutbeispiele

Platzierung von Bauelementen. Einfügung von Leitungsverlänge-rungen.

Testpunkte und Stichleitungen.

Definition von Via-Parametern.

|

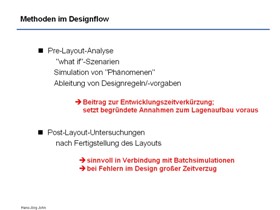

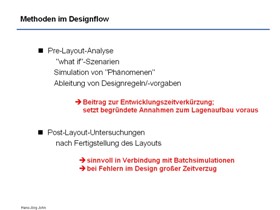

Designflow

SI-Simulationen.

Die Modell-Beschaffung und die Bewertung von Modellen. Simulationsdurchführung.

Pre-Layout-Analysen.

Post-Layout-Analysen.

Die Grenzen von Simulationen.

|

|

|

Ausblick

Impedanz und Laufzeit sowie zugeschnittene Designmethodik reichen für Designs mit Übertragungsraten größer 1 Gbit nicht mehr aus.

Der Übergang zu S-Parametern ist notwendig.

|

Wer wird mit dem ddb1-Seminar

angesprochen?

Die Entwicklung moderner Digitalbaugruppen kann heute nicht mehr nur unter dem Blickwinkel der logischen Funktionalität erfolgen. Dem analogen Verhalten digitaler Signale ist während des gesamten Designprozesses Rechnung zu tragen.

Die Kenntnis und gezielte Berücksichtigung der verschiedenen Signal- und Power-Integrity-Phänomene ist Voraussetzung für eine zuverlässige Funktion und verbesserte Gewährleistung der EMV jeder Logikbaugruppe.

Ziel des 1-tägigen Seminars ist die Vermittlung der physikalischen Ursachen und der Zusammenhänge von Signal- und Power-Integrity-Phänomenen. Es werden Lösungsansätze im Logik- und Layoutbereich sowie Designstrategien im Zusammenhang mit Digitalen-High-Speed-Designs vorgestellt.

Die Eigenschaften digitaler Signale und die Übertragungskonzepte über Transmission Lines werden durch die Erläuterungen der Impedanzberechnungen ergänzt.

Reflexionen auf Leitungen und diverse Kopplungsphänomene werden ausführlich erläutert und um Maßnahmen zur Optimierung der Signalübertragung (Logik, Layout) ergänzt.

Das Timing digitaler Schaltungen und der funktionale Lagenaufbau von Multilayern sind weitere hilfreiche Aspekte des Seminars.

Der Teilnehmer kann nach Absolvierung des Seminars einen Logikentwurf hinsichtlich der Signal- und Power-Integrity bewerten, gezielt Verbesserungsmaßnahmen implementieren und optimale Layoutlösungen erarbeiten.

Außerdem wird er in die Lage versetzt, mögliche Probleme zukünftiger Logikentwicklungen zu erkennen und zu bewerten.

Das Seminar kann für EMV-Ingenieure, Schaltungs-/Logikentwickler, Layouter und Projektleiter empfohlen werden.

Ihr Referent

|

Dr. Hans-Jörg John ist seit 1980 auf dem Fachgebiet Elektromagnetische Verträglichkeit (EMV) tätig und hat in dieser Zeit alle Bereiche der Gewährleistung der EMV in Telekom-, informationstechnischen und Automotiv-Produkten bearbeitet. Er hat über 30 Publikationen zur EMV im In- und Ausland veröffentlicht und war Mitglied des Technical Program Committee des IEEE Workshops "Signal Propagation on Interconnects" von 1997 - 2010.

Von 2003 – 2017 war er bei der Continental Automotive GmbH in Schwalbach tätig. Herr John war in dieser Zeit Leiter des akkreditierten EMV-Labors und verantwortete den EMV-Design-Support am Standort Schwalbach. Seit 2017 ist Dr. John im Ruhestand und arbeitet freiberuflich als Referent.

|

Teilnahmegebühren

Die Teilnahmegebühr beträgt € 520,- pro Person zzgl. MwSt. Enthalten sind ausführliche Seminarunterlagen, ein Mittagessen sowie Pausengetränke. Jeder Teilnehmer erhält ein Zertifikat.

Seminare im Rahmen einer mehrtägigen Veranstaltungsreihe können im Paket gebucht werden. Bei Buchung mehrerer Seminare erhalten Sie eine Ermäßigung von 75,00 Euro pro Seminar.

Da unsere Online-Anmeldeforlulare jeweils für die Buchung einzelner Seminare ausgelegt sind, empfiehlt sich für eine evtl. Paket-Buchung mehrerer Veranstaltungen eine formlose Anmeldung unter anmeldung@leiterplattenakademie.de

Anmeldebedingungen

Aus organisatorischen Gründen ist die Teilnehmerzahl begrenzt. Anmeldungen werden in der Reihenfolge des Eingangs berücksichtigt. Bitte zahlen Sie erst nach Erhalt der Rechnung. Die Rechnung gilt als Anmeldebestätigung, Sie erhalten keine weitere Post. Der Veranstalter behält sich das Recht vor, das Seminar auch nach erfolgter Anmeldebestätigung unter Rückerstattung der Gebühren abzusagen. Nähere Informationen zur Anreise erhalten Sie mit der Rechnung/Anmeldebestätigung.

Eine schriftliche Stornierung der Anmeldung ist bis eine Woche vor dem Veranstaltungstermin gegen eine Bearbeitungsgebühr in Höhe von 40,00 € möglich, danach ist in jedem Falle der gesamte Betrag fällig. Der Teilnehmer kann den Seminarbesuch jedoch innerhalb eines halben Jahres nach dem Seminartermin nachholen.

|

|

|