# Dr. Hans-Jörg John

# **Seminar**

# ddb1

# Design Digitaler Baugruppen unter Berücksichtigung von Signal und Power Integrity Aspekten

Signal Integrity Phänomene

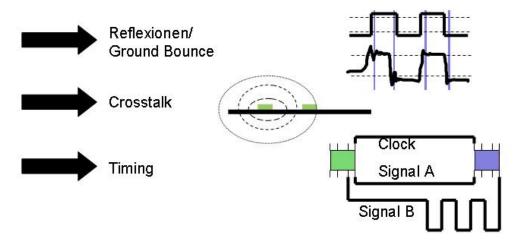

### Drei Phänomene:

# Wer wird mit dem "High Speed Design"-Seminar angesprochen?

Die Entwicklung moderner Digitalbaugruppen kann heute nicht mehr nur unter dem Blickwinkel der logischen Funktionalität erfolgen. Dem analogen Verhalten digitaler Signale ist während des gesamten Designprozesses Rechnung zu tragen.

Die Kenntnis und gezielte Berücksichtigung der verschiedenen Signalund Power-Integrity-Phänomene ist Voraussetzung für eine zuverlässige Funktion und verbesserte Gewährleistung der EMV jeder Logikbaugruppe.

Ziel des 1-tägigen Seminars ist die Vermittlung der physikalischen Ursachen und Zusam-menhänge von Signal- und Power-Integrity-Phänomenen. Es werden Lösungsansätze im Logik- und Layoutbereich sowie Designstrategien im Zusammenhang mit Digitalen-High-Speed-Designs vorgestellt.

Der Teilnehmer kann nach Absolvierung des Seminars einen Logikentwurf hinsichtlich der Signal- und Power-Integrity bewerten, gezielt Verbesserungsmaßnahmen implementieren und optimale Layoutlösungen erarbeiten.

Außerdem wird er in die Lage versetzt, mögliche Probleme zukünftiger Logikentwicklungen zu erkennen und zu bewerten.

Das Seminar kann für EMV-Ingenieure, Schaltungs-/Logikentwickler, Layouter und Projektleiter empfohlen werden.

### Schirmung, Bezugspotential, Signalintegrität

Schlussfolgerung: Das Schirmkonzept (Mechanik) reicht nicht mehr aus! Es müssen zusätzliche (EMV-relevante) Aufwände im Logik- und Bezugspotentialdesign ergriffen werden!

Hans-Jörg Johr

# Einflussgrößen auf EMV

Digitale Systeme müssen sowohl Forderungen zur Störfestigkeit als auch Störemission genügen.

Diese Forderungen lassen sich in der Regel nicht mehr mit einem geschlossenen Schirm erfüllen.

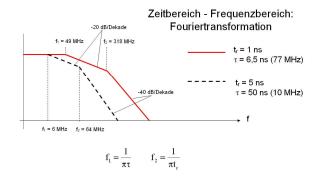

### Frequenzbereich

Hans-Jörg John

# Zeit- und Frequenzbereich

Die Zeitparameter digitaler Signale stehen in einem unmittelbaren Zusammenhang zum Frequenzbereich (Fouriertransformation). Dieser Zusammenhang hat Auswirkungen auf das ausgesendete Spektrum.

### Reale Signalform

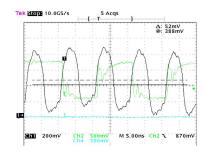

# **Reale Signale**

An Hand realer Signalformen können Konsequenzen zur Funktion aufgezeigt werden. Die Interpretation realer Signalverläufe gibt Hinweise zu mögliche Designfehlern.

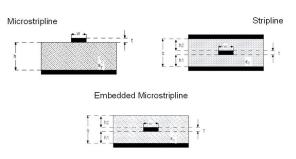

### TLs auf Leiterplatten/physikalisch

Weiterhin Kabel, Steckverbinder etc

Hans-Jörg Johr

# Leitungen auf PCBs

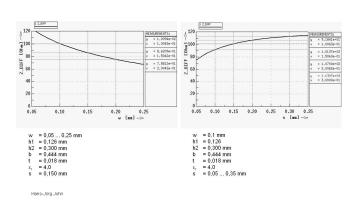

Microstripline, Embedded Microstripline, Stripline. Definition auf Grund der Lage des Leiterzuges in der Leiterplatte. Konsequenzen auf die Berechnung von Impedanzen.

### TLs - elektrische Beschreibung

Ausgangspunkt: infinitesimal kleines Leitungsstück, bestehend aus Hin- und Rückleiter, in dem der Strom als konstant angenommen werden kann:

Anwendung von Maschensatz und Knotenpunktsatz führt zu den

Telegraphengleichungen

# Ersatzschaltbild einer Leitung

Ersatzschaltbilder zur Ableitung der Telegraphengleichungen. Widerstandbelag und Induktivitätsbelag. Ableitungsbelag und Kapazitätsbelag. Primäre Leitungsparameter und sekundäre Leitungsparameter.

### Allgemeingültige Gleichungen

Jede Impedanzberechnung lässt sich auf die Ermittlung des Kapazitätsbelags C' der Leitung zurückführen: (gilt für verlustlose Leitungen/TEM im homogenem Dielektrikum)

$$Z_0 = \sqrt{\frac{L'}{C'}}$$

$$L^{'}*C^{'}=\mu*\epsilon$$

$$Z_{_{0}} = \frac{\sqrt{\mu * \epsilon}}{C^{'}} = \frac{10^{4} * \sqrt{\epsilon_{_{reff}}}}{3C^{'} \left\lceil \frac{pF}{m} \right\rceil}$$

# Wellenwiderstand, verlustlos

Die Berechnung des Wellenwiderstandes für Leitungen in Leiterplatten im verlustlosen Fall wird auf die Ermittlung des Kapazitätsbelages zurückgeführt.

Impedanz, Ausbreitungskonstante

Wellenwiderstand:

$$Z_0 = \sqrt{\frac{R' + j\omega L'}{G' + j\omega C'}}$$

Ausbreitungskonstante:

$$\gamma = \alpha + j\beta = \sqrt{(R' + j\omega L')(G' + j\omega C')}$$

Hans-Jörg John

# Wellenwiderstand, verlustbehaftet

Komplexe Größe, bestehend aus Real- und Imaginärteil bzw. Betrag und Phase. Frequenzabhängige Ausbreitungskonstante.

### Analogie

# Reflexionen 1

Analogie zu Wasserwellen, Stoßstellen, transmittierte und reflektierte Anteile. Ein- und Ausgangswiderstände von integrierten Schaltkreisen. Flankensteilheiten digitaler Signale.

### Reflexionen/Einführung

Alle Verbindungen sind Transmission Lines Reflexionen treten an allen Diskontinuitäten/Stoßstellen auf

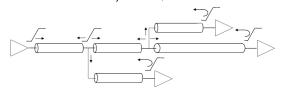

Zwei Techniken:

Terminierung Topologie-Auswahl

Ziel: Nicht eliminieren um jeden Preis, sondern steuern

### Reflexionen 2

Leitungssysteme, Stichleitungen, Sternpunkte.

Daisy-Chain-Verdrahtung.

Terminierungen.

Hin- und rücklaufende Wellen.

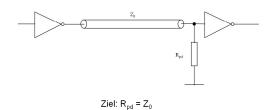

### Terminierungen

Pull down Widerstand

Paralleler Abschluss am Eingang des Empfängers

# **Terminierungsstrategien**

Serienterminierung. Pull-Up und Pull-Down-Terminierung. Thevenin-Terminierung, Diodenterminierung. Ein- und Ausgangswiderstände digitaler Schaltkreise.

### Kopplungsmodell

### Zwei gekoppelte verlustlose Leitungen:

# Crosstalk 1

Ersatzschaltung unabhängig von der Geometrie der Kopplung in der Leiterplatte.

Berechnung.

Koppelkapazität.

Gegeninduktivität.

Leitungsmatrizen.

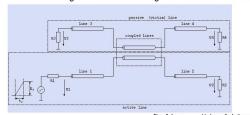

### Crosstalk, Ersatzschaltung

### Ersatzschaltung für die Untersuchung von Crosstalk-Effekten

Parameter:

Verkoppelte Ltg:  $Z_{Le} = 57 \Omega$ ,  $Z_{Lo} = 43 \Omega$ ,  $t_{de} = t_{do} = 1,5 \text{ ns}$ ,  $l_{coupled} = 22,5 \text{ cm}$  $w=0.1mm,\,h1=0.126mm,\,b=0.27mm,\,t=0.018mm,\\ \epsilon_{\ell}=4.0,\,s=0.1mm$

47,6 334,3 m  $[C'] = \begin{cases} 135.9 & -19.3 \\ -19.3 & 135.9 \end{cases} \frac{pF}{m}$

# Crosstalk 2

verkoppelter Leitungsbereich, unverkoppelter Bereich. Störende Leitung und gestörte Leitung.

Forward- und Backward-Kopplung. Common Mode und Even Mode.

### Verkoppelte Leitungen, Diff. Mode

# Differenzielle Impedanz

Verkoppelte Leitungsführung. Gegenphasige Ansteuerung. Etch side coupling. Broad side coupling. Clearance Pair routing. Fieldsolver.

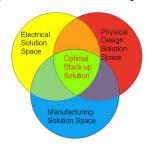

### Freiheitsgrade beim Leiterplattenentwurf

===> Freiheitsgrade für Lp-Entwurf unter Berücksichtigung verfügbarer Materialien!

===> Gegebenenfalls Iterationen notwendig!

ksichtigung

Impedanz, Kopplung, ...

Elektrische Einflussgrößen:

Physikalische Einflussgrößen: Verdrahtungsdichte, Lagenanzahl ...

**Definition von Lagenaufbauten**

Technologische Einflussgrößen: Pressparameter, Ätztoleranzen ...

### Reales Board 2. Fall: bestückte Leiterplatte

Bisher wurde immer von der Impedanz einer unbelasteten Leitung gesprochen

===> diese Impedanz hat im Design nur für Zwei-Punkt-Netze Bedeutung

In einem realen Design kommen Netztopologien vor, die die Impedanz einer Übertragungsstrecke erheblich beeinflussen:

===> Stoßstellen ===> Reflexionen

===> Einsatz von Analogsimulation notwendig

# Impedanz bestückter PCBs

Auswirkungen der Bestückung auf die Impedanz.

Netztopologien.

Eingangskapazität integrierter Schaltkreise.

Simulation von Signalverläufen.

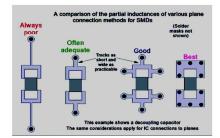

### Abblockkondensatoren, Anschlüsse

# $f_{res} = \frac{1}{2\pi\sqrt{LC}}$

Hane- Pira Joh

## **Abblockkondensatoren**

Stromversorgungssysteme. Stromaufnahme digitaler Schaltungen. Parasitäre Größen von Kondensatoren. Pad-Gestaltung von

Kondensatoren. Buried Capacitance.

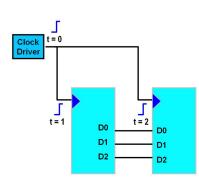

### **Timing Clock-Skew**

- Von Clock-Skew spricht man, wenn verschiedene Bauteile die Clock-Flanke zu unterschiedlichen Zeiten empfangen

- Verlängert bzw. verkürzt die nutzbare Clock-Periode, in Abhängigkeit vom sendenden/empfangenden Baustein

# **Timing**

Datenblattangaben.

Timing Parameter (Skew, Jitter, Laufzeit, Set Up, Hold, Clock to Output).

Common Clock Systeme. Timing-Gleichungen.

### Source Synchronous Designs

- System-(common)Clock wird nicht zur Datenübertragung genutzt

- Bauteile haben einen zusätzlichen bidirektionalen Pin (Strobe), der taktähnliches Signal sendet oder empfängt

# **Source Synchronous Design**

Wirkungsweise. Vorteile und Grenzen. Einflussgrößen. Timing-Gleichungen.

### Layoutbeispiele Theveninabschluss

# | 1578|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638|19 | 1638

Hans-Jörg Joh

# Layoutbeispiele

Platzierung von Bauelementen. Einfügung von Leitungsverlängerungen. Testpunkte und Stichleitungen.

Definition von Via-Parametern.

### Methoden im Designflow

- Pre-Layout-Analyse

"what if"-Szenarien

Simulation von "Phänomenen"

Ableitung von Designregeln/-vorgaben

- → Beitrag zur Entwicklungszeitverkürzung; setzt begründete Annahmen zum Lagenaufbau voraus

- Post-Layout-Untersuchungen nach Fertigstellung des Layout

- → sinnvoll in Verbindung mit Batchsimulationen

- → bei Fehlern im Design großer Zeitverzug

lans-Jörg John

# Designflow

SI-Simulationen.

Modell-Beschaffung und Modell-Bewertung.

Simulationsdurchführung.

Pre-Layout-Analysen.

Post-Layout-Analysen.

Grenzen von Simulationen.

### Ausblick

Übertragungswege/Leiterplatten für Designs mit Datenraten über 1Gb/s sollten nicht nur durch Impedanz und Spezifische Signallaufzeit charakterisiert werden

- ===> Der Übergang zu S-Parametern bietet für die Charakterisierung des Übertragungsweges zusätzliche Informationen

- ===> Insbesondere für differentielle Übertragungswege können Unsymmetrien und Dämpfung über der Frequenz bewertet werden.

## **Ausblick**

Impedanz und Laufzeit sowie zugeschnittene Designmethodik reichen für Designs mit Übertragungsraten größer 1 Gbit nicht mehr aus, der Übergang zu S-Parametern ist notwendig.

### Ihr Referent

**Dr. Hans-Jörg John** ist seit 1980 auf dem Fachgebiet Elektromagnetische Verträglichkeit (EMV) tätig und hat in dieser Zeit alle Bereiche der Gewährleistung der EMV in Tele-kom-, informationstechnischen und Automotiveprodukten bearbeitet. Er hat über 30 Publikationen zur EMV im In- und Ausland veröffentlicht und ist Mitglied

des Technical Program Committee des IEEE Workshops "Signal propagation on Interconnects" von 1997 - 2010.

Von 2003 – 2017 war er bei der Continental Automotive GmbH in Schwalbach tätig. Herr John war in dieser Zeit Leiter des akkreditierten EMV-Labors und verantwortete den EMV-Design-Support am Standort Schwalbach. Seit 2017 ist Dr. John im Ruhestand und arbeitet freiberuflich als Referent.

# Die Leiterplatten Akademie

Die Sicherung des Standortes Deutschland in Europa und der Erhalt der internationalen Wettbewerbsfähigkeit setzt eine systematische und kontinuierliche Qualifikation der Mitarbeiter/innen eines Unternehmens voraus.

Die wirtschaftliche Leistungsfähigkeit einer Industriegesellschaft und ihre technologische Kompetenz am Weltmarkt wird (auch) durch die Qualität ihrer Elektronikprodukte bestimmt.

Das erfordert eine fachlich hochwertige Aus- und Weiterbildung.

Die zentrale Aufgabe der LeiterplattenAkademie ist, das Fachwissen aus den Bereichen der Schaltungsentwicklung, des CAD-Designs, der CAM-Bearbeitung, der Leiterplattentechnologie und der Baugruppenproduktion in Seminaren, Workshops und Tutorials zu vermitteln.

# Seminare und Teilnahmegebühren

Das Tagesseminar "ddb1" wird als freies Seminar durchgeführt, kann für Konferenzen gebucht werden und steht auch als InHouse-Seminar zur Verfügung.

### Freies Seminar

Die Durchführung liegt bei der LeiterplattenAkademie. Die Termine werden via Mailing, eMail, Internet oder Presseveröffentlichungen mitgeteilt. Die Veranstaltungsorte sind in Deutschland, Österreich und der Schweiz. Die Teilnahmegebühr beträgt 520 € zzgl. MwSt. pro Person. Inklusive ausführlicher Seminarunterlagen, Teilnahmezertifikat, Essen und Getränke.

### Konferenz-Seminar

Wenn Sie "ddb1" auf Ihrer Konferenz anbieten möchten, dann sprechen Sie bitte unsere Seminarleitung an.

# InHouse: Unser Seminar in Ihrem Haus

"ddb1" wird auch firmenintern referiert. Sie sparen sowohl Reise- als auch Übernachtungskosten, vor allem jedoch Zeit.

Ab 2.000 € zzgl. MwSt. für 4 Teilnehmer liefern wir Ihnen unseren Referenten "frei Haus". Für jeden weiteren Teilnehmer bis 10 Personen berechnen wir Ihnen 150 € p.P. Weitere Teilnehmer auf Anfrage.

Eine individuelle Themengestaltung mit firmentypischen Schwerpunkten ist selbstverständlich möglich. Bitte stimmen Sie sich mit uns ab: inhouse@leiterplattenakademie.de

Jeder Teilnehmer erhält ausführliche Seminarunterlagen sowie ein Teilnahmezertifikat.

Wir bieten Ihnen 15% Rabatt für InHouse-Seminare in den Monaten Juli und August.

# Die LeiterplattenAkademie

Die LA - LeiterplattenAkademie GmbH ist eine Schulungsund Weiterbildungseinrichtung für die Fachbereiche

Schaltungsentwicklung

CAD-Design

CAM-Bearbeitung

Leiterplattentechnologie

Baugruppenproduktion

Die Akademie versteht sich als Partner für öffentliche Einrichtungen und Unternehmen der Wirtschaft, die in vergleichbaren Feldern engagiert sind.

# LA - LeiterplattenAkademie GmbH Krefelder Straße 18 10555 Berlin

Telefon (030) 34 35 18 99 Telefax (030) 34 35 19 02 eMail info@leiterplattenakademie.de